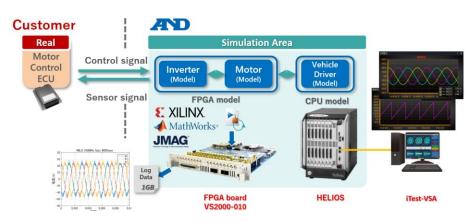

# Motor Hardware-in-the-loop System (HiL)

Cutting edge tool for Motor Controller development

### FPGA Board to run Motor Models at high speeds

- Supports wide range of development process including Motor Control Unit development and verification.

- Interface board equipped with the industry's largest FPGA

- Xilinx Kintex-UltraScale, Large RAM, 200MHz sampling rate

- Equipped with high-speed analog/digital interface.

- supports multiple motor simulations and precise modeling

- Installed on A&D HiLS dedicated platform "HELIOS"

- Motor models can be run as fast a  $1-2\mu sec$  time step

### Ready to use application

- Supports Simulink Models

- FPGA code can be generated using either Xilinx System Generator or HDL Coder

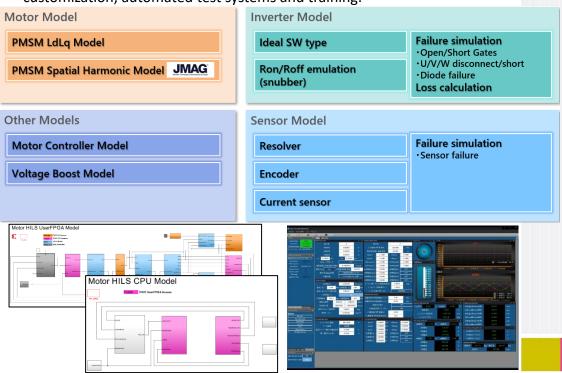

- User can choose appropriate motor model according to application, from precision models such as JMAG-RT motor model, PMSM spatial harmonic model or PMSM LdLq motor model.

- Standard application

- Simulink models for PMSM motor LdLq model, inverter model, sensor model, motor load model, motor controller model, GUI

- A&D also supports engineering such as harness manufacturing, model customization, automated test systems and training.

### Features

- Turnkey solution

- Multiple Platforms

- HELIOS-PRO/HELIOS-LITE

- CPU: Xeon(4core)/core i3(2core)

- VS2000-010-060/115

- VB power supply (600W)

- Equipped with Interface for MCU connection

- Failure Simulation circuits, load emulation

### Application example

- Verification of power train Motor Control Unit for HEV/EV

- Plant model development

# Variety of debugging functions

- DRAM enables signal logging on FPGA up to 100Msps

- Simulation of model failures, open and short circuit, disconnection failures

- Equipped with self-diagnostic function. Makes it is easy to perform daily inspection and identify problems.

## **Board specifications**

New high-end VS2000-010-060/115 FPGA board. Ideal for high-speed and large-scale simulation.

| Spec                            |                 | AD5440-PX27                                                           | VS2000-010-060                                           | VS2000-010-115    |       |

|---------------------------------|-----------------|-----------------------------------------------------------------------|----------------------------------------------------------|-------------------|-------|

| FPGA                            | FPGA            | Kintex7<br>(XC7K410T)                                                 | Kintex UltraScale<br>(KU060)                             | Kintex UltraScale | 1 BAC |

|                                 | FPGA Logic Cell | 306k                                                                  | 725k                                                     | 1451k             |       |

|                                 | DSP             | 1540                                                                  | 2,760                                                    | 5,520             |       |

|                                 | RAM             | 28.6Mb                                                                | 38Mb                                                     | 75.9Mb            |       |

| 1/0                             | AI              | 6+6ch/12.5MHz/14bit                                                   | 4ch/100MHz/16bit                                         |                   |       |

|                                 | AO              | 6+6ch/12.5MHz/14bit                                                   | 14ch/50MHz/14bit                                         |                   |       |

|                                 | DI              | LVTTL: 16ch/25MHz<br>RS422: in 10ch, out 6ch/32MHz                    | 12ch/200MHz                                              |                   |       |

|                                 | DO              | LVDS : in 20ch, out 20ch/125MHz                                       | 4ch/200MHz                                               |                   |       |

| Sampling Frequency              |                 | 125 MHz                                                               | 200 MHz                                                  |                   |       |

| FPGA communication              |                 | X                                                                     | 8 lane ×2 port 5Gbps (Aurora IP)                         |                   |       |

| Fail relay                      |                 | × (External IF BOX)                                                   | 0                                                        |                   |       |

| FPGA development<br>environment |                 | AD5440-PX27 Blockset ( <b>XSG</b> )<br>Matlab R2016b<br>Vivado 2017.3 | VS2000-010 Blockset ()<br>Matlab R2019b<br>Vivado 2020.2 | (SG / HDL coder)  |       |

#### Headquarters

A&D Company, Limited Tokyo, JAPAN Tel: +81 3-5391-6132

Asia

**A&D Technology Inc.** Michigan, U.S.A Tel: +1 734-973-1111

Americas

A&D Technology Trading Co., Ltd. Shanghai, CHINA Tel: +86 21-3393-2340 **A&D Korea Limited** Seoul, KOREA Tel恐+82 2-780-4101

#### Europe

A&D Europe GmbH Darmstadt, GERMANY Tel: +49 6151-3975-250 A&D Europe GmbH UK Branch Abingdon, UK Tel: +44 1235-550-420

# Features

- High speed data logging

- Efficient plant model development

- Failure simulation

- Model and electrical failures

- Self-diagnosis

### Interface

- High-speed I/O interface

- Up to 200MHz sampling

- High-speed communication

### between FPGAs